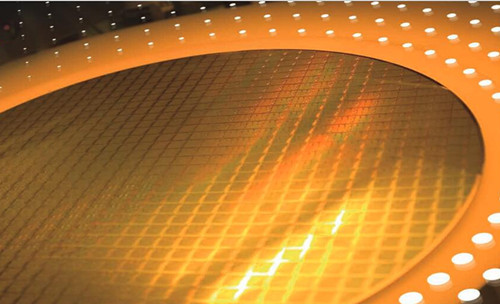

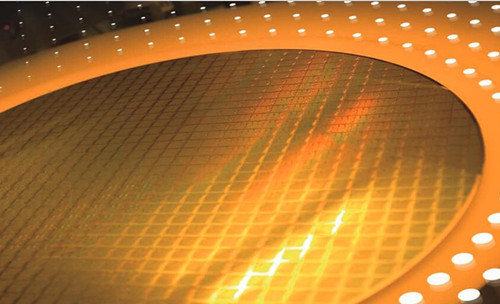

【禾湖财经】6 月 3 日消息,据外媒报道,3nm 制程工艺量产已两年多的台积电,正在推进更先进的 2nm 制程工艺的量产,此前的消息显示台积电的这一制程工艺,已于去年 7 月份开始在新竹科学园区的宝山晶圆厂风险试产,较市场普遍预期的四季度提前了一个季度。

而在最新的报道中,有外媒提到,台积电去年 7 月份开始风险试产的 2nm 制程工艺,目前的良品率已经超过了 90%。

在去年 12 月初,曾有外媒在报道中提到良品率是已超过了 60%,高于台积电的预期。目前超过 90%,也就意味着台积电在风险试产的 2nm 制程工艺的良品率,在半年的时间里提升了约 30 个百分点。

芯片生产过程中的良品率,是晶圆制造中合格芯片与总产量之间的比率,良品率越高,厂商需要承担的不合格产品的成本就越低,分摊到合格芯片上的成本也就越低。可观的良品率也有利于台积电吸引更多客户的订单,增加订单量,进而推升营收。

台积电 2nm 制程工艺风险试产的良品率超过 90%,也就意味着他们的这一制程工艺离量产越来越近。

对于 2nm 制程工艺,台积电董事长兼 CEO 魏哲家在近几个季度的财报分析师电话会议上曾多次提到进展顺利,在按计划推进在 2025 年量产。(海蓝)