文 | 半导体产业纵横

2nm 制程作为摩尔定律延续的关键节点,晶体管密度较 3nm 提升 20%-30%,同等性能下功耗降低 25%-30%,将直接推动 AI 服务器、智能手机等终端设备性能跃升。

日前,三星电子已经完成了全球首款 2nm 移动平台 Exynos 2600 的开发工作,并计划在 9 月底启动该芯片的量产。Exynos 2600 将被应用于明年年初发布的旗舰智能手机 Galaxy S26 系列。

联发科在 9 月 16 日宣布,其 2nm 旗舰 SoC 完成设计流片,将于 2026 年年底进入量产并上市,联发科的 SoC 将由台积电代工。

业界预计苹果也将在 2026 年推出 2nm 制程的芯片,也将由“ 老搭档” 台积电代工。

进入 2025 下半年,2nm 正在越来越近。

先进制程的竞赛中,最大的决定性的因素是良率。在 2nm 的竞赛里,除了传统玩家,还增加了一个新对手,日本的 Rapidus。

2nm 是否有可能成为芯片制造的转折点?

2nm 量产消息不断

在量产进度上,几家代工的进度比拼着不断释出。

三星电子计划从 9 月开始部署人员,在泰勒工厂建立代工生产线。工程师将分两批部署,分别在 9 月和 11 月。此外,已确认正在订购代工生产线建设所需的设备。三星电子也计划在 2025 年下半年开始生产 2nm 芯片。

消息面上,台积电已经从 2025 年 4 月 1 日起开始接受 2nm 订单。随着苹果自研芯片加速向 2nm 工艺制程迈进,明年登场的 A20 也将极大概率是首发采用台积电 2nm 工艺制程的产品。

作为先进制程当之无愧的领先者,台积电已经做好了 2nm 工艺过渡到全面生产的准备。台积电新竹的 P1 工厂已经完成试产工作,展开量产投片,P2 工厂已架设完生产线,两座工厂合计月产能达 3 万至 3.5 万片晶圆。高雄的 P1 工厂最近也进入了量产阶段,月产能为 1 万片晶圆,P2 工厂预计年底试产,两座工厂合计月产能大概在 3 万片晶圆。四座工厂的 2nm 产线月产能将达到 6 万片晶圆。

日本“ 新秀”Rapidus 已于 2025 年 7 月完成了首块 2nm GAA 晶圆的试制,其 2nm 芯片基于 ASML 极紫外 (EUV) 光刻机制造,节点工艺已达到预设的所有电气性能指标。该公司表示,2027 年,Rapidus 位于 IIM-1 工厂的月产能预计可达 2.5 万片晶圆。

2nm 实力分析

首先看技术实力。

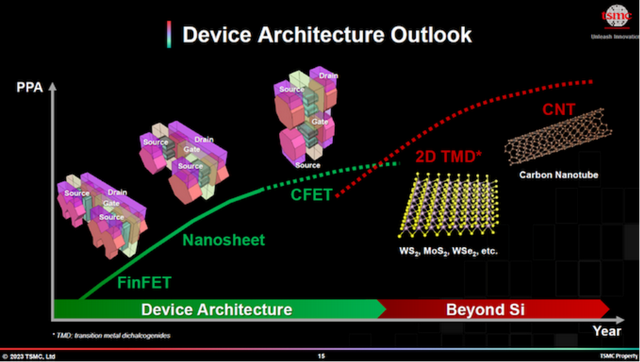

台积电 N2 系列采用 Nanosheet 晶体管技术 (是 GAA 的另一个名字),同时使用 BSPDN(背面供电技术) 助力性能突破。台积电首次在其 2 纳米芯片中采用环栅晶体管架构,标志着一项重大的技术转变。与目前的 3 纳米工艺相比,新节点预计将提供 10% 至 15% 的性能提升、25% 至 30% 的功耗降低以及 15% 的晶体管密度提升。

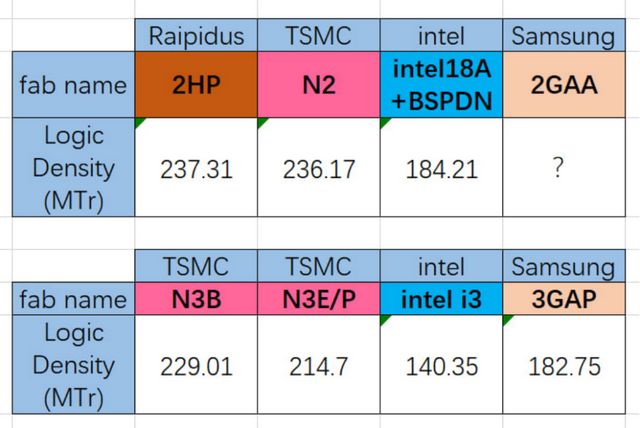

根据第三方机构 TechInsights 的分析,台积电 N2 工艺的高密度 (HD) 标准单元晶体管密度达到了惊人的每平方毫米 3.13 亿个 (313 MTr/mm²)。

三星同样使用 GAA 结构,也搭载了 BSPDN 技术;同时,三星可能引入 2D 材料、CPO(光电共封装) 等技术。

Rapidus 的 2nm 是与 IBM 共同研发的。(作为一个有超多利益相关者的公司,Rapidus 有丰富的技术资源:与 IBM 合作获得 2nm 技术基础;联合比利时 IMEC 获取 EUV 光刻技术;来自佳能、铠甲侠开发的纳米压印技术) 结构上来看,Rapidus 也采用了 GAA 结构,不过 Rapidus 引入了两种不同的栅极减少层 (SLR) 芯片构建工艺。

根据日本芯片制造商 Rapidus 分享的其 2nm 尖端节点 2HP 的数据,进行拟合计算后得出 Rapidus 2HP 工艺逻辑密度可达 237.31MTr/mm2,与台积电同代制程 N2 的 236.17 MTr/mm2 十分接近。

在 2nm 产品正式使用前,很难通过技术路线的选择与应用直接决出谁更胜一筹。不过上文对比也能看出,其实三家的技术路线是相似的。那么决定未来市场的,将会是谁能卖出自己的服务。

对比客户来看。

台积电已经手握头部客户订单。包括苹果、AMD、高通、联发科、博通和英特尔在内的主要客户,均已向台积电“ 下定”2nm。预计台积电将在 2026 年为这些客户大幅增加产量,到 2027 年,包括亚马逊网络服务旗下的 Annapurna Labs、谷歌、Marvell 和比特大陆在内的十多家公司也将进入量产阶段。

台积电 2nm 的定价定为行业最高的 3 万美元,比 3 纳米晶圆的定价高出 50% 至 66%,并且台积电拒绝就价格进行谈判。观察人士认为,台积电的定价策略是在产能受限的环境下刻意控制需求,本质上是鼓励客户争夺有限的生产时段。

三星方面,最新消息显示马斯克将与三星电子合作开发 AI 芯片。对于三星电子来说,Exynos 2600 将成为代工业务的“ 最佳广告”。韩媒表示,Exynos 2600 Geekbench 6 基准测试结果几乎与高通骁龙 8 Elite Gen 2 相当,Exynos 2600 预计还将配备热路径块 (HPB) 模块,以解决长期存在的热问题,同时提高效率和稳定性。

在获客上,Rapidus 似乎是最不利的。不过好在他有相当多的“ 股东”,根据六人法则接触到大客户也不无可能。2025 年 1 月,Rapidus 宣布与博通合作,2nm 芯片产品,计划 6 月向博通提供试产芯片。(不过 9 月,互联网上似乎还没有博通 2nm 的消息。) 此外,日本 AI 企业 Preferred Networks 和 Sakura Internet 也将成为其客户。有媒体表示,黄仁勋也曾暗示过会考虑 Rapidus 代工,不过其原话是“ 供应多样化”,这种“ 暗示” 也许是一种过度解读。

不过,Rapidus 在市场定位上也并不准备与台积电正面竞争大规模标准品,而是聚焦专用芯片市场,抢占机器人、自动驾驶和远程医疗等新兴领域。

再看服务。

台积电将在 2nm 制程节点提供名为“CyberShuttle” 的服务,允许客户在同一片测试晶圆评估芯片。一方面节省客户大量的设计和掩模成本,另一方面加快了测试生产的速度。

三星电子“ 抢单” 的策略很明确:先以价格赢得业务,之后再提高良率。一旦凭借有竞争力的价格和灵活的生产模式锁定客户,就能逐步提高良率。毕竟如果没有大量实际生产的经验,就无法直接提高良率水平。

Rapidus 希望通过生产灵活性来实现差异化。Rapidus 提出单晶圆工艺概念:从设计到晶圆完成的周期可缩短至 50 天 (传统批量-单晶圆混合工艺通常需要约 120 天。) 为满足特定产品的紧急需求,标准交付周期为 50 天,Rapidus 承诺在 2nm 节点实现 15 天的晶圆交付。

2nm 市场潜力

研究公司 Creative Strategies 首席执行官本· 巴贾林 (Ben Bajarin) 此前指出,台积电供应给苹果的 3 纳米晶圆价格已攀升至每片 1.8 万美元,在过去十年中增长了两倍。2 纳米芯片的更高定价凸显了尖端制程技术的稀缺性和不断上升的市场价值。人工智能应用和新兴人工智能数据中心预计将出现巨大增长,以及随之而来的功耗飙升,对 2 纳米芯片的需求将非常巨大。

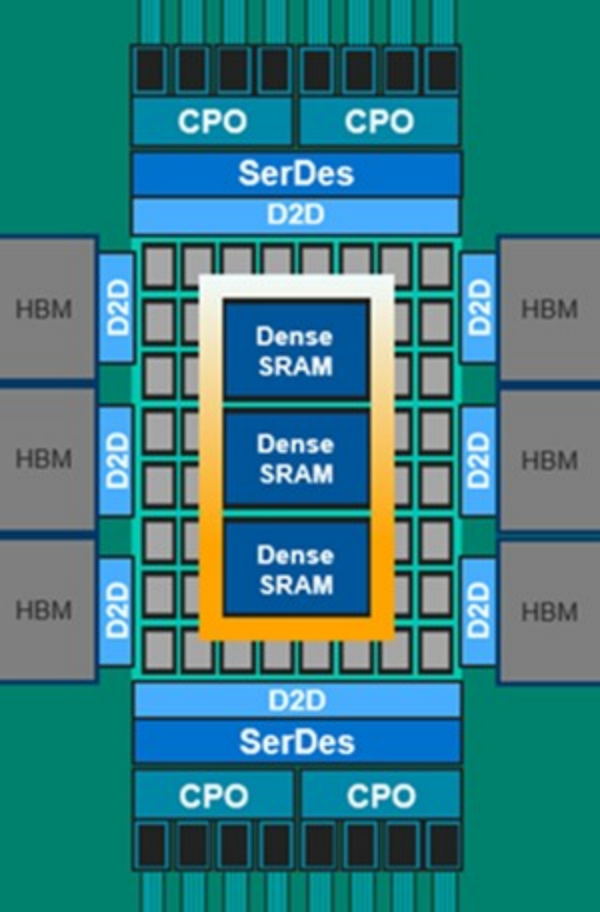

Marvell 声称其定制 SRAM 是业界首款 2nm 定制 SRAM。它旨在提升加速基础设施中内存层的性能,提供高达 6Gbit 的高速内存,从而提升定制 XPU(处理器、加速器、GPU) 和设备的性能。此外,在相同密度下,它还能显著降低内存功耗和芯片面积。

该公司的 SRAM 比类似密度的标准片上 SRAM 功耗低 66%,运行频率高达 3.75GHz,这是 AI 集群和数据中心管理其能源足迹和有效冷却组件的关键指标。

通过 2nm 技术,SRAM 可以与逻辑芯片集成在同一块芯片上。来源:Marvell Technology

背后的赢家

在先进制程的竞争中,不可忽视的是背后赢家 ASML。

台积电已于 2024 年下半年推出高 NA EUV 设备,以加速其 2 纳米工艺路线图的推进。2nm 将继续扩大高数值孔径 EUV 系统的部署,以在 2 纳米以下时代保持竞争力。这些设备由 ASML 独家生产,受荷兰出口管制,每年产量仅为五到六台,凸显了其稀缺性和战略重要性。

每台高数值孔径 EUV 设备的成本超过 3.5 亿美元,是现有 EUV 系统 (约 1.5 亿美元) 价格的两倍多。然而,这些新一代设备将透镜数值孔径从 0.33 提升至 0.55,从而能够实现 2 纳米以下的超精细电路图案化,同时提高良率并降低半导体生产的缺陷率。

业内分析显示,三星 2 纳米试产良率目前在 30% 至 50% 之间,落后于台积电已超过 60% 的良率。三星希望通过扩展其高 NA EUV 设备阵容,缩小这一差距,提高生产效率,增强竞争力。

英特尔通过联合投资获得了六台 EXE:5200 设备的优先使用权,而 SK 海力士最近宣布在其位于京畿道利川 M16 晶圆厂安装 EXE:5200B 系统,成为首家在生产中部署该设备的内存芯片制造商。

ASML 宣布 EXE:5200B 将于 2025 年正式量产供应,这预示着全球先进半导体技术的竞争将更加激烈。

总结来看,台积电依旧具备金字招牌,稳中求进;三星则依靠“ 情绪价值” 希望拿回曾经失去的信任;而 Rapidus 则希望依靠“ 背后的人” 拿下一篇蓝海。

2nm 制程的竞赛,谁领跑,谁出局?也许在 2026 年,答案就会揭晓。

更多精彩内容,关注钛媒体微信号 (ID:taimeiti),或者下载钛媒体 App